[CDI] Senior IP subsystem SoC architect

SiPearl

Canton de Massy, France

8 days ago

Role details

Contract type

Permanent contract Employment type

Full-time (> 32 hours) Working hours

Regular working hours Languages

English Experience level

SeniorJob location

Remote

Canton de Massy, France

Tech stack

Communications Protocols

Computer Programming

Computer Engineering

Microarchitecture

High-Level Architecture

Python

PCI Express

Software Prototyping

Subsystems

Tcl (Programming Language)

Scripting (Bash/Python/Go/Ruby)

Application Specific Integrated Circuits

Physical Design

Job description

In this role, you will work closely with the Design, Verification, Physical Implementation and Software teams to define, drive and evolve IP, subsystem and SoC architectures aligned with performance, cost, manufacturability and market requirements.

You will act as a technical authority and architectural reference, contributing to strategic decisions, cross-team alignment, external partnerships and team development.

About the missions

- Define IP, subsystem and SoC architectures to meet performance, silicon area, cost and manufacturing constraints

- Break down architectures into functional sub-blocks and write high-level architecture specifications, including interfaces and configuration mechanisms

- Participate in commercial IP selection and process technology choices

- Provide detailed definitions of software programming and configuration interfaces

- Support RTL, physical design, verification, virtual and software prototyping teams by clarifying architectural intent and constraints

- Review microarchitecture specifications, verification strategies and validation plans

- Interface closely with marketing and product teams to ensure architectural alignment with roadmap and customer needs

- Contribute to technology intelligence, monitoring standards, market trends and emerging technologies

- Represent the company at seminars, conferences and technical forums, and share key learnings internally

- Take ownership of work packages in collaborative and partnership projects, acting as a technical point of contact

- Coordinate project deliverables and contribute regularly to partner exchanges

- Mentor, coach and technically supervise junior engineers, trainees and service providers

- Contribute to effort estimation, milestone planning, onboarding and training programs

- Support the manager in supervising team members within the defined scope

Requirements

Do you have experience in SoC?, * Extensive experience in complex chip architecture and microarchitecture

- Strong background in electronic engineering, microelectronics or computer engineering

- Ability to translate market and product requirements into robust technical architectures

- Excellent communication skills, with the ability to explain complex concepts to diverse audiences

- Strong leadership, mentoring and cross-functional collaboration skills

- High level of autonomy, accountability and strategic thinking

- Professional proficiency in English in an international environment

- Scientific rigor, attention to detail and strong analytical capabilities

Experience in the following areas is a strong plus

- Core architecture design, PCIe, UCIe, memory interfaces

- Cache architectures, memory consistency models, Network-on-Chip (NoC)

- Communication protocols and system-level integration

- Advanced ASIC design flows and semiconductor technologies

- Strong software background and hardware/software co-design

- Proficiency in scripting languages (Python, TCL, etc.)

- Leadership roles in collaborative or multi-partner projects, ️AssessFirst personality test - no need to worry, there is no wrong or right answer; our goal is to see beyond your resume (45')

About the company

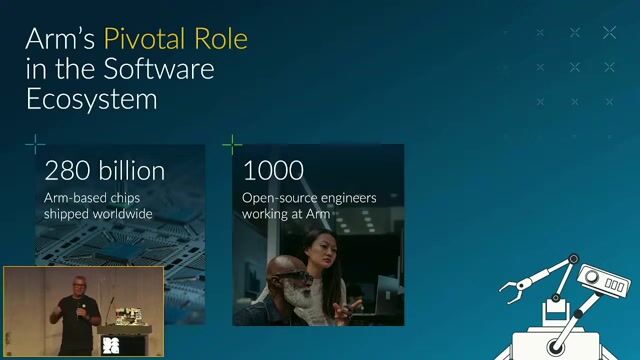

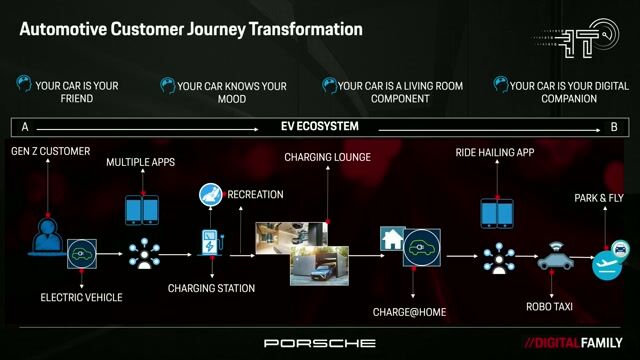

SiPearl is the European fabless designer of sovereign secure high-performance energy-efficient CPUs for HPC, AI and data centres. These CPUs will help address strategic challenges in the fields of security, defence, medical research, energy, climate and engineering with a reduced environmental footprint.

In June 25, SiPearl completed the design of the most complex CPU ever designed in Europe, Rhea1. Featuring 80 Arm Neoverse V1 cores, with 61 billion transistors, it is currently in production at TSMC. Sipearl CPUs will equip the two first European exascale supercomputers belonging to EuroHPC JU: Rhea1 will be integrated into the JUPITER machine based in Germany and Rhea2 will be part of Alice Recoque in France.

Incubated within the European Processor Initiative (EPI) consortium and seed-funded by the European Union, SiPearl employs almost 200 people in :

* France (Maisons-Laffitte, Grenoble, Massy, Sophia Antipolis),

* Spain (Barcelona)

* and Italy (Bologna)

Following a €130 million Series A, the company has launched its Series B round.