Staff Performance Modelling Engineer

Role details

Job location

Tech stack

Job description

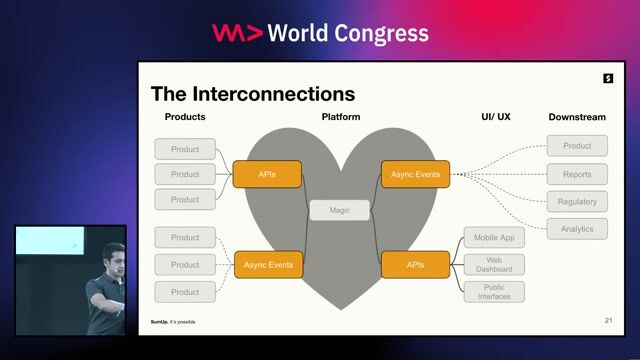

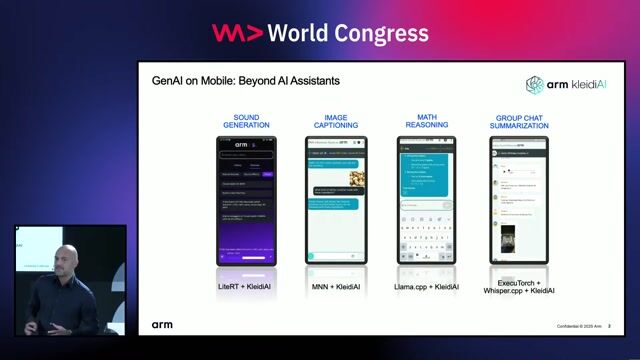

In this role, your primary responsibility will be performance analysis of next-generation Interconnect IP. You will work closely with architecture, design, and modeling teams to evaluate design trade-offs, identify bottlenecks, improve modeling accuracy, and drive performance validation.

About System IP

This position is part of the Interconnect Product Team.

The Interconnect team develops Arm's CoreLink Interconnect IP - scalable, high-performance NoCs designed for intelligent connected systems across markets such as mobile, IoT, networking infrastructure, and automotive. Our solutions are optimized for

Responsibilities

- Drive performance analysis of Interconnect IP, including advanced Network-on-Chip designs.

- Evaluate architectural design trade-offs to influence performance and scalability.

- Investigate and identify performance bottlenecks through deep analysis and performance correlation against RTL emulation.

- Collaborate closely with architecture, RTL, and modeling teams to validate performance targets and provide actionable feedback.

- Contribute to C++-based performance models to support performance studies and system-level simulations.

- Build and extend infrastructure and tooling for insightful performance data visualization and analysis.

- Support system-level performance studies in collaboration with internal teams across Arm.

- Contribute to evolving performance analysis methodology and standard processes across Arm's System IP group.

Requirements

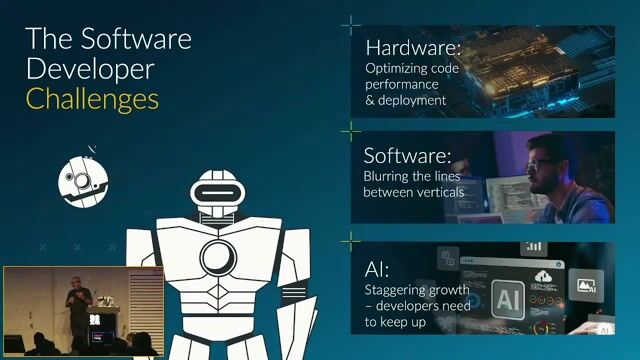

We are looking for an experienced and highly motivated engineer to join one of the hard-working teams within Systems Engineering, with a strong focus on performance analysis. This role is ideal for someone passionate about deep performance investigations, bottleneck identification, and data-driven architectural insights - alongside developing supporting C++ models., * Strong hands-on experience in performance analysis and architectural performance tuning.

- Proficiency in C++ programming, particularly performance modeling and simulation.

- Solid understanding of computer architecture, particularly memory subsystems and interconnects.

- Python scripting experience for automation and data analysis.

"Nice To Have" Skills and Experience :

- Experience with SoC-level performance analysis and tools.

- Familiarity with memory subsystem micro-architecture and performance implications.

- Experience with Verilog/SystemVerilog RTL, including analysis and debugging in collaboration with design teams.

- Working knowledge of AMBA protocols and transaction-level modeling (SystemC/TLM).

- Exposure to Verilog/SystemVerilog and interaction with RTL design and verification teams.

- Experience mentoring other engineers in performance analysis or modeling efforts.