SOC Memory Subsystem Architect

Role details

Job location

Tech stack

Job description

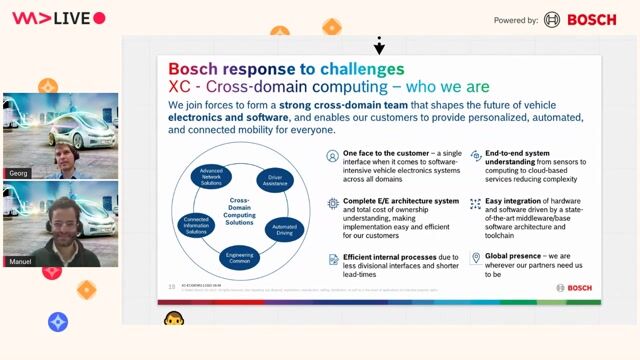

As a SoC Memory Subsystem Architect, you will play a key role in shaping the future of our premium chipsets by defining and driving the development of innovative SoC memory and cache subsystems. This is a high-level, technical contributor position that requires a strong foundation in architecture principles, as well as in-depth understanding of memory subsystems, including memory hierarchies, interfaces, controllers, and caches. Your expertise will enable you to propose and implement new, efficient SoC memory architectures that meet the demands of our cutting-edge products.

- You identify, propose, and deliver new SoC memory architectures and features for premium mobile and related product platforms.

- You contribute to high-impact deliverables, with the freedom to experiment and explore novel ideas to challenge existing norms and push the boundaries of what is possible.

- You create detailed designs and specifications for memory subsystems, including memory interfaces, controllers, and caches.

- You analyze PPA trade-offs and optimize memory subsystem performance, power consumption, and area utilization to meet system requirements.

- You work closely with software, hardware, and validation teams to ensure memory subsystem designs meet system requirements and are properly integrated

- You create and maintain detailed documentation of memory subsystem designs, including architecture, implementation, and verification plans.

- You inspire high performance, mentor junior engineers, foster trust, and promote a culture of ownership culture and open communications.

- You stay up-to-date with emerging memory technologies and recommend their adoption in SoC designs.

Requirements

- 20+ years of experience with a Bachelor's Degree in Computer Science/Engineering, or 18+ years of experience with a Master's Degree, or 16+ years of experience with a PhD

- Extensive experience designing and developing complex digital systems and SoC memory architectures.

- Expertise in memory hierarchies, memory interfaces (e.g., DDR, LPDDR, HBM), and memory controllers is crucial.

- Detailed knowledge of cache subsystems including caching policies and understanding the tradeoffs of latency, bandwidth and hierarchies

- Experience with cache coherence protocols and bus protocols - CHI/ACE/AXI

- Knowledge of memory scheduling, bandwidth management, and latency optimization.

- High familiarity with existing and emerging JEDEC memory standards

- Strong written and verbal communication skills

- Experience with the Android ecosystem and analysis tools is a plus

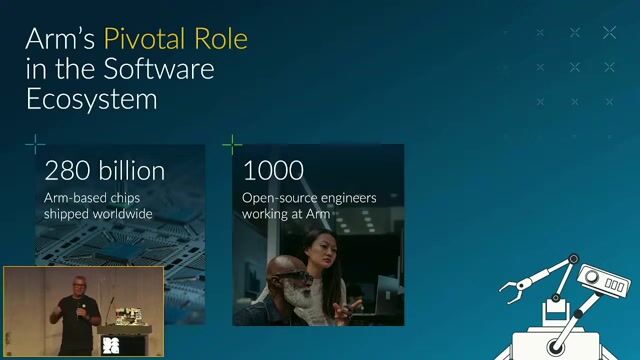

- Experience with Arm architecture and ecosystem is a plus, This position requires the ability to access information subject to U.S. export control restrictions. Applicants must have the ability to access export-controlled information or be eligible to receive a government authorization to access export-controlled information.

Benefits & conditions

At Samsung - SARC/ACL, base pay is one part of our total compensation package and is determined within a range. This provides the opportunity to progress as you grow and develop within a role. The base pay range for this role is between $221,700 and $364,800. Your actual base pay will depend on variables that may include your education skills, qualifications, experience, and work location. This is an exempt position, which is not eligible for overtime pay under the Fair Labor Standards Act (FLSA).

Samsung employees have access to benefits including: medical, dental, vision, life insurance, 401(k), free onsite lunch, employee purchase program, tuition assistance (after 6 months), paid time off, student loan program, wellness incentives, and many more. In addition, regular full-time employees (salaried or hourly) are eligible for MBO bonus compensation, based on company, division, and individual performance.

Additionally, this role might be eligible to participate in long term incentive plan and relocation.